Architecture for Streaming Applications

# Members of the graduation committee:

Prof. dr. ir. G. J. M. Smit

Dr. ir. J. Kuper

Dr. ir. A.B.J. Kokkeler

Dr. ir. R. Langerak

University of Twente (promotor)

University of Twente (assistant-promotor)

University of Twente

Prof. dr. J.L. Hurink

University of Twente

University of Twente

Prof. dr. K. Svarstadt Norwegian University of Science and Technology

Prof. dr. dr. h. c. ir. M.J. Plasmeijer University of Nijmegen

Prof. dr. P.M.G Apers University of Twente (chairman and secretary)

# UNIVERSITY OF TWENTE.

Faculty of Electrical Engineering, Mathematics and Computer Science, Computer Architecture for Embedded Systems (CAES) group

CTIT Ph.D. Thesis Series No. 14-322 Centre for Telematics and Information Technology PO Box 217, 7500 AE Enschede, The Netherlands

This research is conducted as part of the Sensor Technology Applied in Reconfigurable systems for sustainable Security (STARS) project (www.starsproject.nl)

Copyright © 2014 Anja Niedermeier, Enschede, The Netherlands. This work is licensed under the Creative Commons Attribution-NonCommercial 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc/4.0/.

This thesis was typeset using LaTeX, TikZ, and GNU Emacs. This thesis was printed by Gildeprint, The Netherlands.

ISBN 978-90-365-3732-2

ISSN 1381-3617; CTIT Ph.D. Thesis Series No. 14-322

DOI 10.3990./1.9789036537322

# A Fine-Grained Parallel Dataflow-Inspired Architecture for Streaming Applications

# Dissertation

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

Prof. Dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Friday 29<sup>th</sup> August, 2014 at 12:45

by

Anja Niedermeier

born on October 25<sup>th</sup>, 1982 in Böblingen, Germany

# This dissertation has been approved by:

Prof. dr. ir. G. J. M. Smit (promotor)

Dr. ir. J. Kuper (assistant-promotor)

Dr. ir. A.B.J. Kokkeler (assistant-promotor)

# **Abstract**

Data-driven streaming applications are quite common in modern multimedia and wireless applications, like for example video and audio processing. The main components of these applications are Digital Signal Processing (DSP) algorithms.

These algorithms are not extremely complex in terms of their structure and the operations that make up the algorithms are fairly simple (usually binary mathematical operations like addition and multiplication). What makes it challenging to implement and execute these algorithms efficiently is their large degree of fine-grained parallelism and the required throughput.

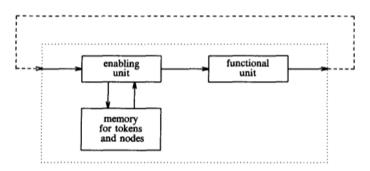

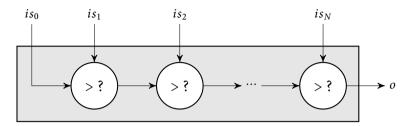

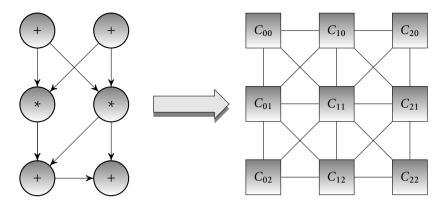

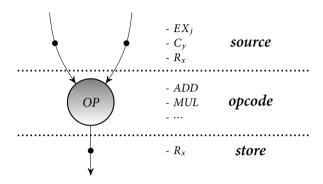

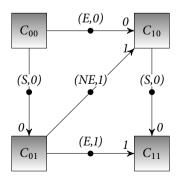

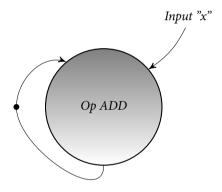

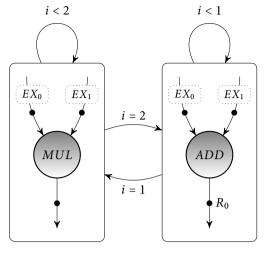

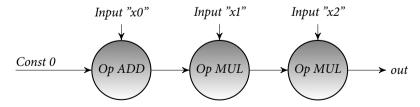

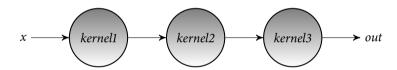

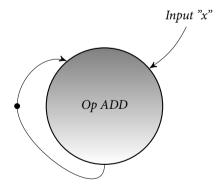

DSP algorithms can usually be described as dataflow graphs with nodes corresponding to operations and edges between the nodes expressing data dependencies. On the edges, data travels in the form of tokens. A node *fires* as soon as all required input data has arrived at its input edge(s). One firing consists of consuming the input data (i.e. input tokens), executing the desired operation, and producing the output data (i.e. output tokens). Usually, input data to the dataflow graph is provided as a stream of tokens. As a consequence, a well-behaved dataflow graph keeps executing as long as input data arrives.

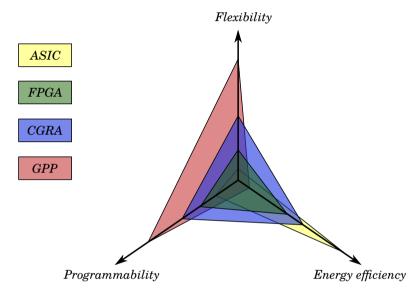

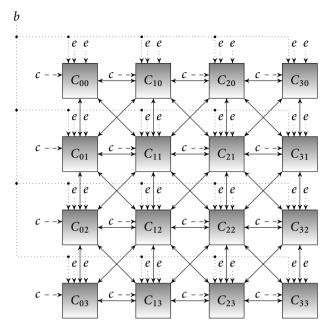

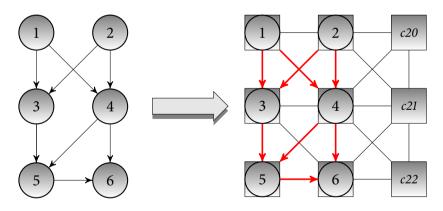

To execute DSP algorithms efficiently while maintaining flexibility, coarse-grained reconfigurable arrays (CGRAs) can be used. CGRAs are composed of a set of small, reconfigurable cores, interconnected in e.g. a two dimensional array. Each core by itself is not very powerful, yet the complete array of cores forms an efficient architecture with a high throughput due to its ability to efficiently execute operations in parallel.

To program CGRAs, usually an architecture-specific subset of C is defined which is then used to specify and implement algorithms on the respective CGRA. However, the C programming paradigm was not developed to specify algorithms that contain a large degree of fine-grained parallelism. Instead, it was designed to implement sequential algorithms on single-core architectures.

In this thesis, we present a CGRA targeted at data-driven streaming DSP applications that contain a large degree of fine-grained parallelism, such as matrix manipulations or filter algorithms. Along with the architecture, also a programming language is presented that can directly describe DSP applications as dataflow graphs which are then automatically mapped and executed on the architecture.

In contrast to previously published work on CGRAs, the guiding principle and inspiration for the presented CGRA and its corresponding programming paradigm is the dataflow principle. Three main aspects can be named here:

- A DSP algorithm is represented as a dataflow graph with nodes corresponding to operations and edges between the nodes corresponding to data dependencies.

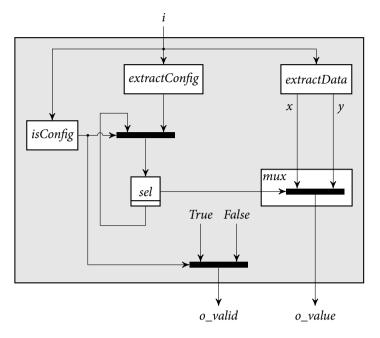

- 2. The configuration and execution principles of the cores in the architecture are based on dataflow principles, i.e. a core starts its execution based on the availability of data (i.e. availability of input tokens).

- 3. Dataflow graphs can be explicitly expressed in the programming language.

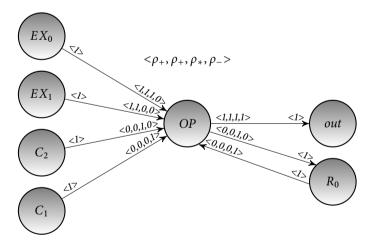

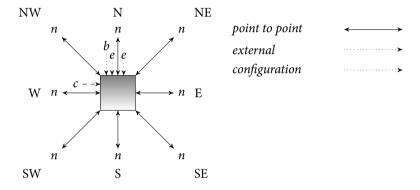

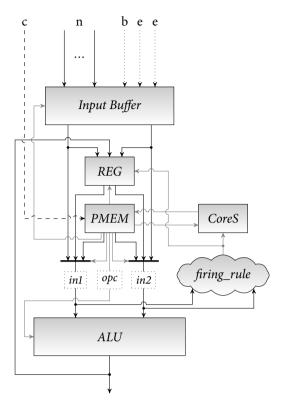

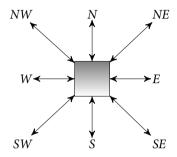

The presented architecture is a CGRA with small, reconfigurable cores which communicate via point-to-point links. Each core is independent from its neighbours, i.e. there is no central entity controlling the complete array, instead, control is local to each core. The execution mechanism of the cores in the architecture is data-driven, i.e. it adopts the firing rule known from dataflow. A core starts its execution based on the availability of input data. Hence, no fixed schedules and no program counters are required, which makes the presented CGRA fundamentally different from previously presented CGRAs that rely on an imperative programming paradigm.

The architecture has been implemented using C $\lambda$ aSH, a hardware description language and compiler that can generate synthesisable VHDL code from a Haskell specification. Describing hardware with C $\lambda$ aSH enables a designer to describe hardware in terms of its structure.

The programming language for the presented architecture can describe a DSP algorithm as a dataflow graph. The grammar of the language resembles a dataflow structure, i.e. it contains constructs for dataflow nodes which are used to construct dataflow graphs. The language is implemented as an embedded language in Haskell. Therefore, Haskell's powerful features like recursion and higher order functions can be used. This is very beneficial for describing an algorithm in terms of its structure and data dependency, in particular for representing the fine-grained parallelism as present in the targeted application domain. By using the same design language for both the architecture and the programming language, no switching between environments is required and the same type definitions can be used.

The result of this work is a completely integrated framework targeted at streaming DSP algorithms, consisting of a CGRA, a programming language and a compiler. The complete system is based on dataflow principles, in particular the firing rule, i.e. execution is triggered by the availability of input data, not determined by a fixed schedule. We evaluate the framework by implementing a number of commonly used DSP algorithms, e.g. a FIR filter, a dot product and an FFT kernel, on the architecture using the presented programming language. We conclude that by using an architecture that is based on dataflow principles and a corresponding programming paradigm that can directly express dataflow graphs, DSP algorithms can be implemented in a very intuitive and straightforward manner.

# Samenvatting

Data gedreven stromende applicaties zijn te vinden in moderne multimedia en draadloze toepassingen, zoals bijvoorbeeld bij video en audio verwerking. De grootste componenten binnen dergelijke applicaties zijn algoritmes voor digitale signaalverwerking (DSP, Eng: *Digital Signal Processing*).

Dit soort algoritmes is niet complex qua structuur en operaties binnen deze algoritmes zijn vrij simpel (meestal zijn dit binaire operatoren zoals optelling en vermenigvuldiging). De uitdaging bij het implementeren en efficiënt uitvoeren van dit soort algoritmes is het benutten van de hoge mate van fijnmazig parallellisme en het behalen van de vereiste doorvoersnelheid.

DSP-algoritmes kunnen meestal worden beschreven als *dataflow*-grafen waarbij *nodes* operaties voor stellen en de *edges* tussen de nodes de gegevensafhankelijkheden tussen operaties. Data worden doorgegeven via een edge in de vorm van *tokens*. Een node *vuurt* zodra alle vereiste invoer beschikbaar is op de inkomende edges. Een vuring bestaat uit het consumeren van de invoer (de inkomende tokens), het uitvoeren van de bijbehorende operatie en ten slotte het produceren van uitvoer (uitgaande tokens). De invoer voor een dataflow graaf bestaat uit een stroom van tokens. Als gevolg zal een correcte dataflow-graaf uitgevoerd worden zolang er invoer beschikbaar is.

Om DSP-algoritmes efficiënt te kunnen uitvoeren met behoud van flexibiliteit kunnen grofmazige herconfigureerbare *arrays* (CGRA, Eng: *Coarse-Grained Reconfigurable Arrays*) gebruikt worden. CGRA's bestaan uit kleine, herconfigureerbare rekenkernen welke aan elkaar verbonden zijn in bijvoorbeeld een tweedimensionale reeks. Alhoewel elke kern op zichzelf niet bijster krachtig is, vormt de complete reeks een efficiënte architectuur met een hoge doorvoersnelheid door operaties parallel uit te voeren.

Om CGRA's te programmeren wordt meestal een architectuur-specifieke deelverzameling van C gedefinieerd welke gebruikt kan worden om algoritmes voor de betreffende CGRA te implementeren. Echter, het programmeerparadigma van C is niet ontworpen voor het specificeren van algoritmes met een hoge mate van fijnmazig parallellisme maar voor sequentiële algoritmes voor architecturen met een enkele rekenkern.

In dit proefschrift presenteren we een CGRA voor data gedreven stromende DSP-applicaties met een hoge mate van fijnmazig parallellisme, zoals bij matrix bewerkingen of filter algoritmes. Behorende bij de architectuur presenteren we een programmeertaal voor het beschrijven van DSP-applicaties als dataflow-grafen welke automatisch afgebeeld en uitgevoerd kunnen worden.

In tegenstelling tot eerder gepubliceerde werken over CGRA's is het principe voor de gepresenteerde CGRA en bijbehorende programmeerparadigma gebaseerd op het dataflow principe. Drie hoofdaspecten zijn:

- Een DSP-algoritme is beschreven als een dataflow-graaf waarbij nodes overeenkomen met operaties en de edges tussen nodes overeenkomen met gegevensafhankelijkheden.

- 2. De principes bij configuratie en uitvoering op de rekenkernen in de architectuur zijn gebaseerd op dataflow-principes; een rekenkern begint met uitvoeren zodra alle benodigde invoer-tokens beschikbaar zijn.

- Dataflow-grafen kunnen expliciet worden uitgedrukt in de programmeertaal.

De gepresenteerde architectuur is een CGRA met kleine, herconfigureerbare rekenkernen welke via punt-naar-punt verbindingen communiceren. Elke rekenkern is onafhankelijk van zijn buren; er is geen centrale besturing voor de hele reeks omdat elke rekenkern zelfstandig kan handelen. Het uitvoeringsmechanisme van de rekenkernen is data-gestuurd omdat de vuringsregels van dataflow worden gevolgd. Een rekenkern begint met zijn uitvoering zodra alle benodigde invoer beschikbaar is. Hierdoor is er geen vast schema voor de uitvoering van alle taken en zijn geen programma-stappentellers nodig waardoor de gepresenteerde CGRA fundamenteel anders is dan voorheen gepresenteerde CGRA's welke gebruik maken van een imperatief programmeerparadigma.

De architectuur is geïmplementeerd met C $\lambda$ aSH, een hardware beschrijvingstaal en vertaler die synthetiseerbare VHDL-broncode kan genereren van een Haskell specificatie. Het beschrijven van hardware met behulp van C $\lambda$ aSH geeft een ontwerper de mogelijkheid om hardware uit te drukken qua structuur.

De programmeertaal voor de gepresenteerde architectuur kan een DSP-algoritme beschrijven als een dataflow-graaf. De grammatica van de programmeertaal lijkt op een dataflow-structuur; het bevat constructies voor het beschrijven van dataflow nodes welke in de constructie van een graaf gebruikt worden. De programmeertaal is geïmplementeerd als een geëmbedde taal in Haskell. Hierdoor kunnen krachtige mogelijkheden uit Haskell zoals recursie en hogere-ordefuncties gebruikt worden. Dit is zeer gunstig voor het beschrijven van een algoritme qua structuur en gegevens afhankelijkheid, met name voor fijnkorrelig parallellisme zoals aanwezig in het beoogde toepassingsgebied. Door het gebruik van dezelfde ontwerptaal voor zowel de architectuur en de programmeertaal is geen omschakeling tussen omgevingen vereist en kunnen dezelfde type definities gebruikt worden.

Het resultaat van dit werk is een compleet geïntegreerd raamwerk voor stromende DSP-algoritmes bestaande uit een CGRA, programmeertaal en een compiler. Het hele systeem is gebaseerd op dataflow principes, met name de vuringsregel waarbij uitvoering wordt gestart bij de beschikbaarheid van invoergegevens en niet volgens een vast schema. We evalueren het raamwerk door middel van de implementatie van een aantal gangbare DSP-algoritmes zoals een FIR-filter, een *dot product* en een FFT-*kernel* op de gepresenteerde architectuur en met behulp van de gepresenteerde programmeertaal. We concluderen dat het gebruik van een architectuur, gebaseerd op dataflow-principes en bijbehorend programmeerparadigma voor het uitdrukken van dataflow-grafen, zorgt voor een intuïtieve en ongecompliceerde aanpak voor het implementeren van DSP-algoritmes.

# Acknowledgements

Now that this thesis is almost finished with only a few last bits and pieces to be finished, it is finally time to write the acknowledgements. What a rewarding moment after more than four years of work!

Whenever people ask me how I ended up in Twente of all places, the story I have to tell them is not very straightforward. In 2002, I started to study Electrical Engineering at the University of Karlsruhe, and in 2006, I went as an Erasmus student to Trondheim, Norway, for a year. During that year I decided to stay in Trondheim and finish my studies there. At the end of the two-year masters in Trondheim, I got the opportunity to do my M.Sc. project at IMEC in Eindhoven. During my stay at IMEC, I decided that I would like to stay in research a little longer and try to pursue a PhD. My supervisor at IMEC heard of that and hinted that the CAES group at the University of Twente was looking for PhD students. I then sent an open application to Gerard Smit, who invited me over for an interview and on the next day I got the offer to start a PhD in Twente, which I was really happy about. And that is how I ended up in Twente.

My initial research topic in Twente was *off-chip communication*. But after a while it became clear to me that this was not really a topic I was particularly interested in so I decided to switch to something else. I discussed the matter with Gerard Smit and André Kokkeler and luckily they gave me the freedom to look for a new topic myself. After talking to a few people (especially Kenneth Rovers) and reading a bit I decided that I wanted to investigate dataflow related architectures, a topic which eventually resulted in this thesis. At this point I also want to thank Gerard for giving me the freedom to follow my interests during my PhD and investigate this really cool field of architecture design with dataflow principles.

While I was looking for a new research topic, Jan Kuper gently pointed me towards the wondrous world of functional programming. Even though I had heard about that programming paradigm at some point during my studies, I never actually worked with it. But since Jan (and a few more of the group) seemed to be very convinced of it I got curious. As a result, a great part of this thesis was written using Haskell, and, even though it sometimes gave me a headache, it was certainly fun to work with. So, at this point, a big thanks to Jan for showing me a new perspective to the world of programming and of course also thanks to the many discussions

In 2010 I joined P-NUT, the PhD network of the University of Twente, for a few activities and eventually joined their board in 2011. Not only was this a lot of fun, but it was also a valuable experience and I met a lot of cool people in the board of P-NUT and during all our activities. I certainly miss being in the board and would like to thank all of you who I had the pleasure of organising stuff together or just having fun with in the last years!

In the beginning of 2012, I went back to Trondheim for three months. What happened between March 18 to 20 is still hard to grasp and even harder to accept. Nature can be cruel, without mercy and unpredictable and technology cannot always save you. Florian, even though you are not here anymore, I want to thank you for the time we had and all the inspiration you gave me. Without you I would not be who I am now.

I am very grateful for the enormous amount of support of friends and colleagues I received afterwards, and I really want to thank all of you. Yahya, Sven, Sylvie and Kata, your company meant a great deal to me in the few remaining days in Trondheim. Back in Twente, my colleagues from the CAES group were really nice and helpful, which is certainly not something to take for granted. In particular I want to thank Robert, Jan, Gerard, Marlous, Philip, Rinse, Koen and Berend. Besides my colleagues, I really want to thank Silja, Christina and Sarah for being there for me so many times. It would have been much more difficult without you.

But despite everything, I had a nice time doing my PhD in the CAES group, and two really nice office mates, Robert and Timon. I had the opportunity to travel to nice conferences and summer schools, and learned a lot about the academic life. I would like to thank Gerard Smit, André Kokkeler and Jan Kuper for their guidance and discussions during my PhD. And of course, a thesis cannot be written without support. So at this point, I would like to thank our secretaries for their help, and a big thanks to Christiaan for all the C $\lambda$ aSH support, to Philip for the help and loads of little hints concerning LaTeX and to Marco for all the little but very important tips for the last bits and pieces of the thesis itself. Also I would like to especially thank Silja and Robert for being my paranymphs during my defense, it means a lot to me.

And of course I would like to thank a very important person in my life, Berend. Thanks for your support in finishing up this thesis and for so many other things, not only for translating the abstract to Dutch:)

Schließlich möchte ich mich noch von ganzem Herzen bei meinen Eltern bedanken, die mich immer ermuntert und unterstützt haben, egal in welche Stadt oder welches Land ich ging. Ihr habt mir stets das Gefühl gegeben dass alles machbar ist und mir nie Steine in den Weg gelegt.

Anja Niedermeier Enschede, August 2014

# Contents

| l | Int | Introduction                                                                                                                                                              |                       |  |  |  |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

|   | 1.1 | Research goal  1.1.1 Architecture  1.1.2 Target application domain  1.1.3 Programming of the system  1.1.4 Design of the complete system                                  | 3<br>3<br>4<br>4<br>5 |  |  |  |

|   | 1.2 | Key requirements                                                                                                                                                          | 5                     |  |  |  |

|   | 1.3 | Structure of this thesis                                                                                                                                                  | 5                     |  |  |  |

|   | 1.4 | Summary of our contributions                                                                                                                                              | 6                     |  |  |  |

| 2 | Bac | CKGROUND                                                                                                                                                                  | 9                     |  |  |  |

|   | 2.1 | Dataflow principles                                                                                                                                                       | 9<br>9<br>10<br>11    |  |  |  |

|   | 2.2 | Dataflow based programming languages  2.2.1 General properties of dataflow languages  2.2.2 Advantages and disadvantages of dataflow languages  2.2.3 Concrete languages: | 11<br>12<br>13<br>14  |  |  |  |

|   | 2.3 | Dataflow machines                                                                                                                                                         | 16                    |  |  |  |

|   | 2.4 | Coarse-grained reconfigurable arrays (CGRAs)  2.4.1 General principle  2.4.2 Architectures                                                                                | 18<br>18<br>18        |  |  |  |

|   | 2.5 | Conclusions                                                                                                                                                               | 21                    |  |  |  |

| 3 | Design Methods and Tools |                                                  |          |  |  |

|---|--------------------------|--------------------------------------------------|----------|--|--|

|   | 3.1                      | Introduction to Haskell                          | 23       |  |  |

|   |                          | 3.1.1 Syntax                                     | 24       |  |  |

|   |                          | 3.1.2 Higher order functions                     | 24       |  |  |

|   |                          | 3.1.3 Types                                      | 26       |  |  |

|   |                          | 3.1.4 Algebraic datatypes                        | 28       |  |  |

|   |                          | 3.1.5 Data structures                            | 28       |  |  |

|   |                          | 3.1.6 Choice                                     | 30       |  |  |

|   |                          | 3.1.7 Lambda expressions                         | 32       |  |  |

|   | 3.2                      | CλaSH                                            | 32       |  |  |

|   |                          | 3.2.1 Differences between CλaSH and pure Haskell | 33       |  |  |

|   |                          | 3.2.2 State                                      | 34       |  |  |

|   |                          | 3.2.3 Define a component                         | 35       |  |  |

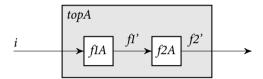

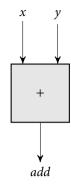

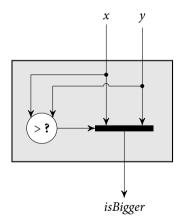

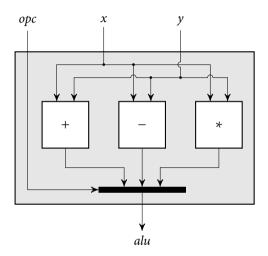

|   |                          | 3.2.4 Composition of components                  | 35       |  |  |

|   |                          | 3.2.5 Examples                                   | 36       |  |  |

|   |                          | 3.2.6 Simulation                                 | 43       |  |  |

|   |                          | 3.2.7 VHDL generation                            | 44       |  |  |

|   | 3.3                      | Conclusions                                      | 46       |  |  |

|   |                          |                                                  |          |  |  |

| 4 | Cor                      | NCEPTUAL BASIS FOR THE DATAFLOW CGRA             | 47       |  |  |

| • | 4.1                      | Motivation                                       | 47       |  |  |

|   |                          |                                                  |          |  |  |

|   | 4.2                      | Conceptual view on the algorithm                 | 48       |  |  |

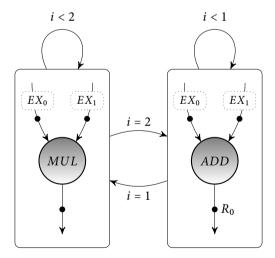

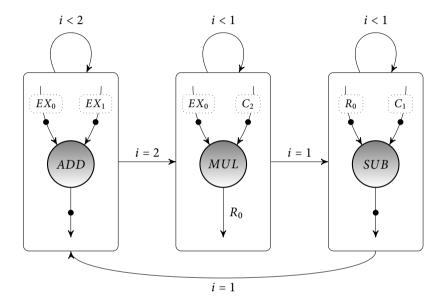

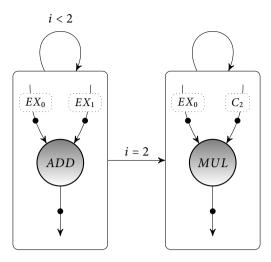

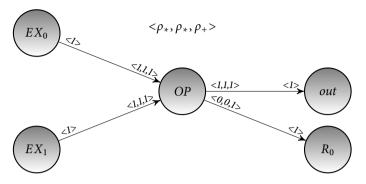

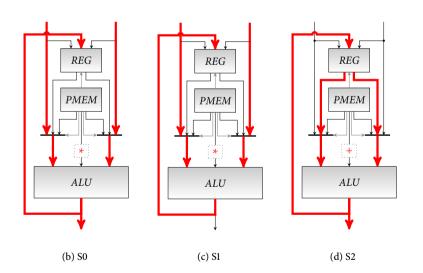

|   |                          | 4.2.1 Local view                                 | 49<br>49 |  |  |

|   |                          | 4.2.2 Extended local view                        | 54       |  |  |

|   | 4.2                      |                                                  |          |  |  |

|   | 4.3                      | Conclusions                                      | 55       |  |  |

|   |                          |                                                  |          |  |  |

| 5 | Arc                      | CHITECTURE                                       | 57       |  |  |

|   | 5.1                      | Overview and goal                                | 57       |  |  |

|   | 5.2                      | Implementation                                   | 58       |  |  |

|   | 5.3                      | General principles                               | 58       |  |  |

|   |                          | • •                                              |          |  |  |

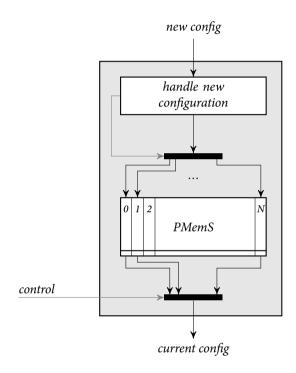

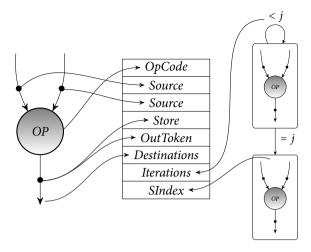

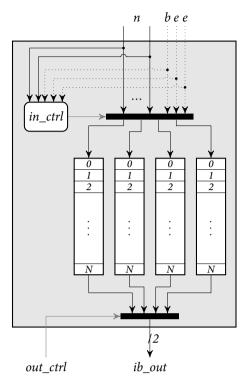

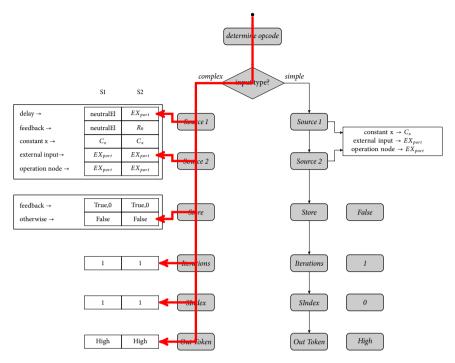

|   | 5.4                      | Architecture - hardware                          | 58<br>59 |  |  |

|   |                          | 5.4.1 Requirements                               |          |  |  |

|   |                          | 5.4.2 Interconnect 5.4.3 Number datatypes        | 60<br>61 |  |  |

|   |                          | 5.4.4 Core                                       | 61       |  |  |

|   |                          |                                                  |          |  |  |

|   | 5.5                      | Example of a configuration                       | 72       |  |  |

|   | 5.6                      | Design decisions                                 | 75       |  |  |

|   | 5.7                      | Synthesis results                                | 76       |  |  |

|   | 5 0                      | Conclusions                                      | 76       |  |  |

| 6 | Pro | GRAMMING LANGUAGE AND COMPILER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77         |  |  |  |  |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

|   | 6.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77         |  |  |  |  |

|   | 6.2 | The grammar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78         |  |  |  |  |

|   |     | 6.2.1 The constructors of the EDSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80         |  |  |  |  |

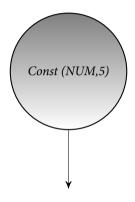

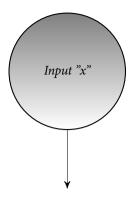

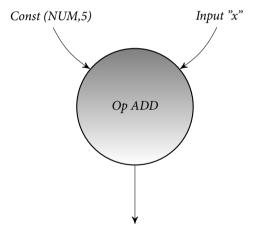

|   |     | 6.2.2 Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82         |  |  |  |  |

|   | 6.3 | Streaming notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84         |  |  |  |  |

|   | 6.4 | The abstract syntax tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |  |  |  |  |

|   | 6.5 | Mapping to the architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |  |  |  |  |

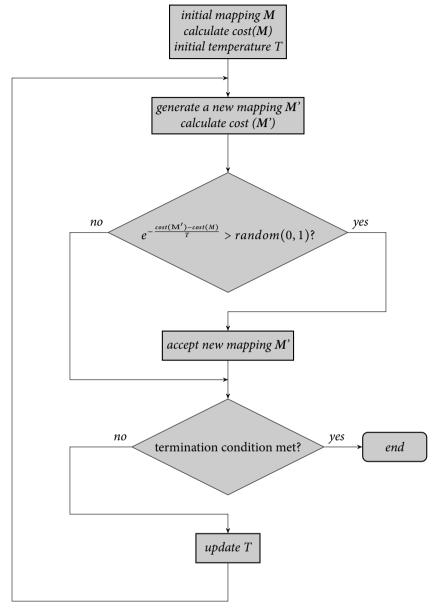

|   |     | 6.5.1 Simulated annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87         |  |  |  |  |

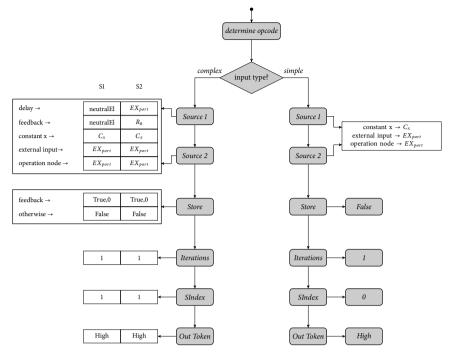

|   | 6.6 | Code generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89<br>90   |  |  |  |  |

|   |     | 6.6.2 Adding the routing information to the configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96         |  |  |  |  |

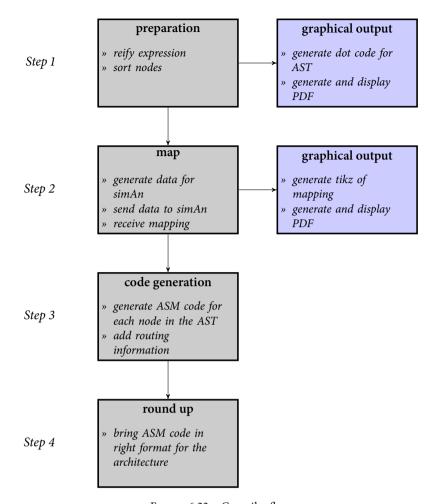

|   | 6.7 | The complete compilation flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97         |  |  |  |  |

|   | 6.8 | Design decisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99         |  |  |  |  |

|   | 6.9 | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99         |  |  |  |  |

|   | 0.5 | 001.01.01.01.01.01.01.01.01.01.01.01.01.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |  |  |  |  |

| 7 | DES | SIGN FLOW AND CASE STUDIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101        |  |  |  |  |

|   | 7.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101        |  |  |  |  |

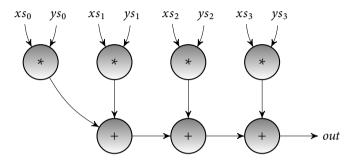

|   | 7.2 | Showcase algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 101        |  |  |  |  |

|   | 7.3 | Implementation of the algorithm by the user                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102        |  |  |  |  |

|   |     | 7.3.1 Implementing the algorithm in Haskell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102        |  |  |  |  |

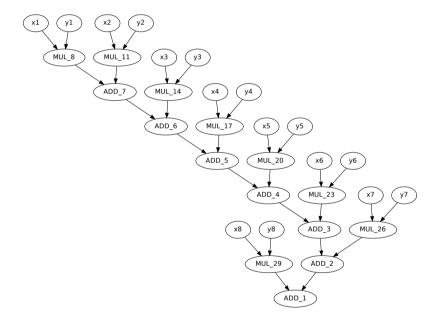

|   | 7.4 | Start the compilation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103        |  |  |  |  |

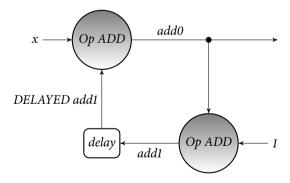

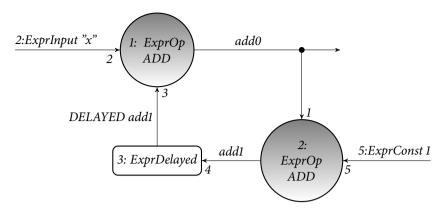

|   |     | 7.4.1 Graphical output of the expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104        |  |  |  |  |

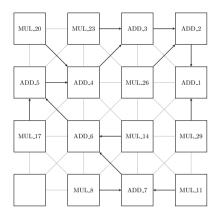

|   |     | 7.4.2 Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104        |  |  |  |  |

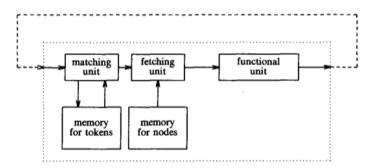

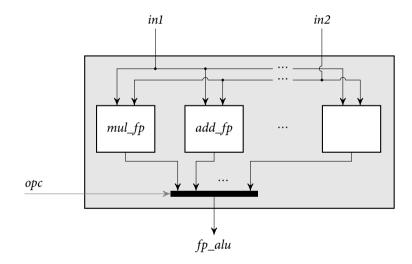

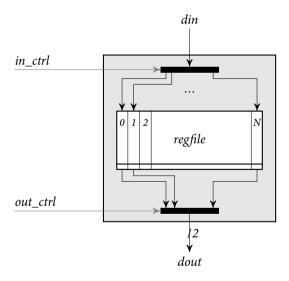

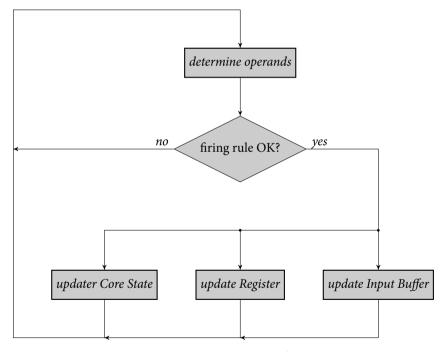

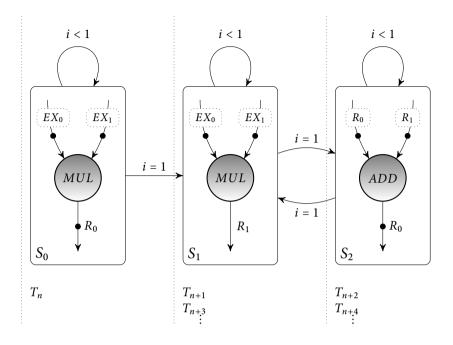

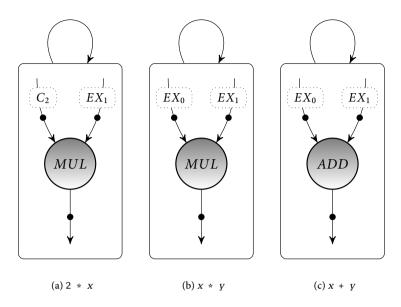

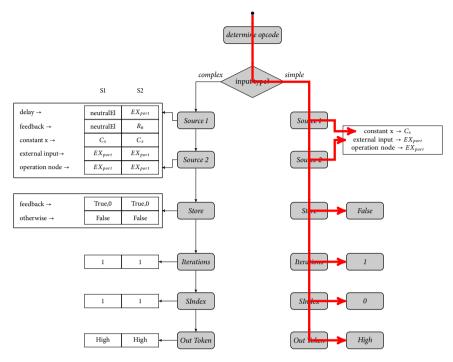

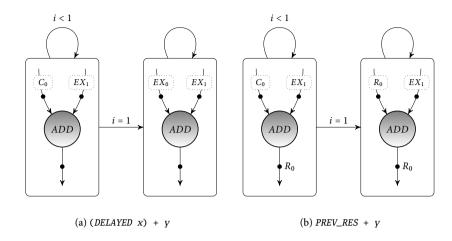

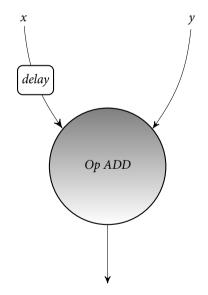

|   |     | 7.4.3 Graphical output of the mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105        |  |  |  |  |